#### **DUPLO Deliverable D2.2**

# Integration report of RF and antenna self-interference cancellation techniques

Project Number: 316369

Project Title Full-Duplex Radios for Local Access – DUPLO

Deliverable Type: PU

**Contractual Date of Delivery:** October 31, 2014 **Actual Date of Delivery:** October 31, 2014 Editor(s): Björn Debaillie (IMEC) Author(s): Cristina Lavín, Carmen Palacios (TTI); Björn Debaillie, Benjamin Hershberg, Barend van Liempd (IMEC); Eric Klumperink, Dirk-Jan van den Broek (UT). Work package: WP2 **Estimated person months:** 20 Security: ΡU Nature: Report Version: 1.0

**Keyword list:** full-duplex, design, antenna, RF circuits and systems, duplexer, self-interference, isolation, cancellation, polarized antenna, electrical balance, active cancellation

DUPLO WP2 D2.2 1 / 76

Abstract: Full-duplex sets challenging requirements for wireless communication radios, in particular their capability to prevent receiver sensitivity degradation due to self-interference (transmit signals leaking into its own receiver). The DUPLO project mainly targets solutions for wireless radios to facilitate full-duplex operation in compact commercially attractive communication devices. This work package focusses on the design of small form-factor antenna structures and RF circuits which offer a substantial self-interference isolation or rejection and support integration with other solutions developed in the DUPLO project (e.g. baseband cancellation). Previously published techniques mainly rely on physical dimensions (i.e., antenna spacing) and/or require bulky components. Therefore, they are not applicable in the DUPLO project, as they hamper dense integration in compact radios.

The previous deliverables of this workpackage [1, 2] and the JSAC publication [3] report and motivate the architecture selection, design and initial measurements of the first antenna and RF prototype, and presents a theoretical link budget calculation methodology to derive the system component design requirements. Current document evaluates these earlier achieved results and develops, designs and fabricates new prototypes to improve the performance or to investigate the elimination of potential show-stoppers.

This document continues on the three designs presented in D2.1 [1, 3]. The first design covers a dual-polarized microstrip patch antenna, where a second prototype has been design and fabricated. This prototype offers improved bandwidth and has a smaller form factor compared to the first prototype. This second prototype has been designed based on parametric optimization and the measured performance has been reported. The second design covers a duplexer based on a tunable electrical balance circuit. Some severe limitations have been observed with the first electrical balance prototype in terms of bandwidth and linearity. To investigate if these limitations can be overcome, a second prototype has been designed and fabricated. This second prototype implements a highly linear balance network with multiple degrees of freedom to create multiple tunable isolation notches. The third design covers an active cancellation network operating on RF signals, capable of cancelling dynamically the self-interference. The performance of different cancellation networks, including components with variable gain, phase and time delay, with gain, are evaluated in combination with the antenna solution developed in this project.

These designs have been well received by the scientific community as this work has been accepted for publication in several peer-reviewed IEEE conferences. Compared to state-of-the-art, the developed designs differ mainly in terms of form-factor and integration potential in compact or portable radio system devices.

**Disclaimer:** This document reflects the contribution of the participants of the research project DUPLO. The European Union and its agencies are not liable or otherwise responsible for the contents of this document; its content reflects the view of its authors only. This document is provided without any warranty and does not constitute any commitment by any participant as to its content, and specifically excludes any warranty of correctness or fitness for a particular purpose. The user will use this document at the user's sole risk.

DUPLO WP2 D2.2 2 / 76

# **Executive Summary**

This DUPLO WP2 deliverable D2.2 entitled "Integration report of RF and antenna self-interference cancellation techniques" presents the second and final phase of the design and implementation of the prosed antenna and RF circuit solutions, enabling compact full-duplex wireless radio devices. This document evaluates the results achieved during the first phase, which are reported in D2.1 [1] and in the JSAC publication [3] and develops, designs and fabricates new prototypes to improve the performance or to investigate the elimination of potential show-stoppers.

The key design requirements in both phases are to minimize the RF self-interference and to target small form-factor antenna/RF solutions which can be implementable in compact radio devices. These requirements are however contradictory as dense integration and compact form-factor designs reduce the physical spacing between the transmitting and receiving elements/circuits/signals. In state-of-the-art full-duplex radio system design, this physical spacing is generally exploited to increase the self-interference isolation.

The presented techniques focus on *antenna* and *RF circuit* techniques only, and in combination with *transceiver* and *digital cancellation* techniques, an overall self-inference rejection of about 100dB is targeted for a mid-end scenario as described in D1.1 [4]. Based on the link budget calculation over realistic scenarios presented in D2.3.1 [2] and [3], the RF self-interference isolation factor should exceed 45 to 50dB over a bandwidth of 10MHz.

This document continues on the three designs presented in D2.1 [1, 3] covering a dual-polarized microstrip patch antenna design, and a tunable electrical balance duplexer design and an active cancellation network design to be applied at RF. This document describes how the performance of the designs can be improved, and validates these improvements based on the fabrication and measurements of new prototypes.

- A second dual-polarized microstrip patch antenna prototype has been designed, fabricated and measured. This prototype builds on similar topology as the first prototype and offers the same functionalities, but provides better performance (e.g. bandwidth) and is smaller in size. A parametric optimization methodology has been applied to specify the design parameters of the second prototype. The second prototype is smaller (60x60x8mm) and offers wider bandwidth capabilities with an SI isolation of 49dB over 10MHz and 42dB over 80MHz. Over 10MHz, antenna gain is higher than 6.5dB and offers a 3dB beamwidth of more than 70 degrees with an antenna efficiency of more than 75%. The isolation characteristics and robustness can be improved together with the active cancellation described in this document. This antenna prototype is used for integration in the DUPLO proof-of-concept demonstrator.

- Measurements in the electrical balance duplexer (EBD) first prototype indicated two main issues potentially hampering the exploitation for full-duplex operation. These issues are the limited bandwidth and the limited linearity of the balance network. These issues are described in this document and a second prototype has been designed and fabricated to investigate the capability to resolve these specific issues. To avoid the complexity overhead, this second prototype includes a tunable balance network only, without the transformer. This second prototype is implemented in SOI technology to leverage the linearity, and an additional degrees of tunability has been implemented in the balance network to trade-off the average SI isolation with the isolation bandwidth. The second prototype has been implemented in 0.18um SOI CMOS technology and covers an area of 0.9mm² only. This design offers an extremely high linearity (IIP3 > 70dBm) and can handle relatively high transmission power (e.g. 27dBm) without considerable heating-up.

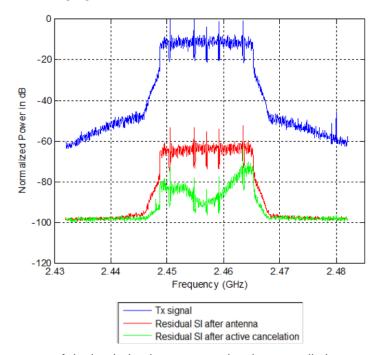

- The work on the active cancellation, initiated in D2.1 [1] has been continued and extended. This document details the design and component selection of the cancellation network and presents an automatic tuning method to control and tune the network to its optimal configuration in an efficient way. The active cancellation method has been verified based on measurements in combination with the second dual-polarized antenna prototype described in this document. These measurements

DUPLO WP2 D2.2 3 / 76

indicate an additional SI reduction of 15dB in addition to the isolation provided by the antenna solution. The active cancellation performance has been also analyzed including a variable time delay element in the cancellation network. This work is further continued in WP5.

The presented work mainly differentiates with state-of-the-art in terms of form factor and integration potential in compact or portable radio system devices. In this document, the developed techniques are compared with state-of-the-art solutions which apply similar techniques or topologies. With respect to the antenna, the usage of a single radiating element with orthogonal polarizations is hardly described in literature for full-duplex application, although dual-polarized antennas are frequently used in many others wireless communication systems. These dual-polarized elements enable to create compact form-factor full-duplex antennas. Their main limitation in full-duplex scenarios, is the small robustness of their isolation performance when external objects are close to the antenna. To increase this robustness, we developed the active cancellation network. With respect to the duplexer, electrical balancing designs for full-duplex are hardly described in literature. In FDD applications, full-duplex are more frequency considered, but our design outperforms the performances presented in literature. The designs presented in this document are well received by the scientific community as this work has been accepted for publication in several peer-reviewed IEEE conferences as described in chapter 6, and the comparison with state-of-the-art is given in chapter 7.

The results from WP2 are shared with the other workpackages within the DUPLO project as described in chapter 5.

DUPLO WP2 D2.2 4 / 76

# **Authors**

| Partner                                                   | Name                   | Email                        |

|-----------------------------------------------------------|------------------------|------------------------------|

| TTI Norte, SL (TTI)                                       | Cristina Lavín         | clavin@ttinorte.es           |

|                                                           | Carmen Palacios        | mcpalacios@ttinorte.es       |

| Interuniversitair Micro-Electronica<br>Centrum vzw (IMEC) | Björn Debaillie        | bjorn.debaillie@imec.be      |

| Centrum vzw (nvice)                                       | Benjamin Hershberg     | benjamin.hershberg@imec.be   |

|                                                           | Barend van Liempd      | barend.vanliempd@imec.be     |

| Universiteit Twente (UT)                                  | Eric Klumperink        | e.a.m.klumperink@utwente.nl  |

|                                                           | Dirk-Jan van den Broek | j.d.a.vandenbroek@utwente.nl |

DUPLO WP2 D2.2 5 / 76

# **Table of Contents**

| 1. | INTF                | RODUCT                     | TION                                                                                                                                          | 10 |

|----|---------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2. | FUL                 | L-DUPL                     | EX TECHNOLOGY AT ANTENNA-LEVEL                                                                                                                | 12 |

|    | 2.1.                | INTROD                     | DUCTION ON ANTENNA TECHNIQUES                                                                                                                 | 12 |

|    |                     | 2.1.1.<br>2.1.2.           | Overview of the proposed solution  Evaluation of the first DUPLO antenna prototype                                                            |    |

|    | 2.2.                | SECON                      | D DUAL-POLARIZED ANTENNA PROTOTYPE                                                                                                            | 15 |

|    |                     | 2.2.1.<br>2.2.1.<br>2.2.2. | Dual-polarized antenna design details  Second prototype implementation and evaluation  Performance evaluation of the second antenna prototype | 21 |

| 3. | FUL                 | L-DUPL                     | EX TECHNOLOGY AT RF CIRCUIT LEVEL                                                                                                             | 27 |

|    | 3.1.                | THE EL                     | ECTRICAL-BALANCE DUPLEXER CONCEPT AND TARGET SPECIFICATIONS                                                                                   | 27 |

|    |                     | 3.1.1.<br>3.1.2.           | Limitations of the first prototype                                                                                                            |    |

|    | 3.2.                | SECON                      | D PROTOTYPE: HIGHLY-LINEAR, HIGHER-DIMENSIONAL BALANCE NETWORK                                                                                | 31 |

|    |                     | 3.2.1.<br>3.2.2.<br>3.2.3. | Technology considerations: SOI CMOS versus bulk CMOS  Design considerations                                                                   | 32 |

|    |                     | 3.2.4.                     | Summary                                                                                                                                       |    |

| 4. | ACTIVE CANCELLATION |                            |                                                                                                                                               |    |

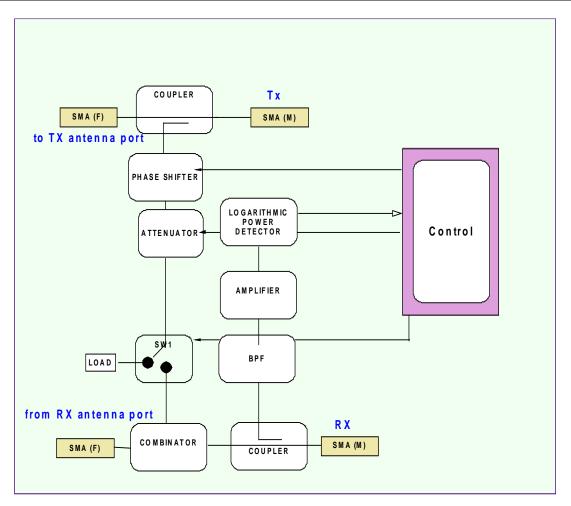

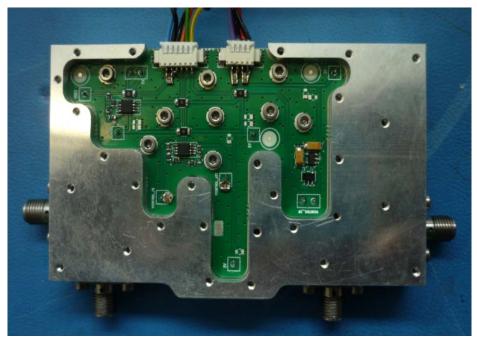

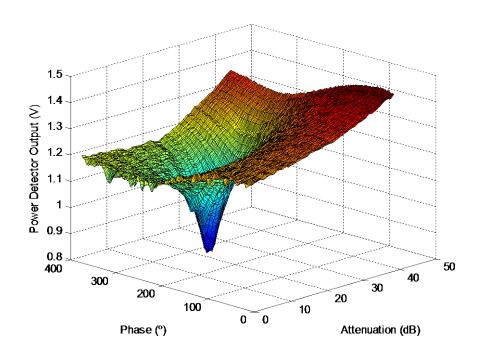

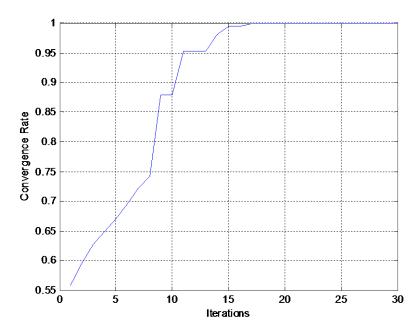

|    | 4.1.                | _                          | DUCTION TO ACTIVE CANCELLATION CONCEPT                                                                                                        |    |

|    | 4.2.                |                            | CANCELLATION NETWORK IMPLEMENTATION AND INTEGRATION                                                                                           |    |

|    |                     | 4.2.1.<br>4.2.2.<br>4.2.3. | Circuitry design and implementation  Auto-tuningIntegration in DUPLO demonstrator                                                             | 53 |

|    | 4.3.<br>4.4.        |                            | DUAL-POLARIZED ANTENNA AND ACTIVE CANCELLATION NETWORK VALIDATION                                                                             | 56 |

|    |                     | 4.4.1.<br>4.4.2.           | Impact of passive suppression on self-interference response Active cancellation including variable delay line                                 |    |

| 5. | INTE                | EGRATIO                    | ON AND VALIDATION POTENTIAL                                                                                                                   | 64 |

| 6. | DISS                | SEMINA                     | TION                                                                                                                                          | 66 |

| 7. | STA                 | TE-OF-1                    | THE-ART AND FUTURE OPPORTUNITIES                                                                                                              | 68 |

|    | 7.1.<br>7.2.        |                            | PORT FD ANTENNA SYSTEMS                                                                                                                       |    |

| 8. | SUN                 | IMARY A                    | AND CONCLUSIONS                                                                                                                               | 73 |

| 0  | DEE                 | EDENC                      | EC                                                                                                                                            | 75 |

# **Acronyms and Abbreviations**

3D three dimensions

AC alternating current

ANT antenna

BW bandwidth

C capacitance

cm centimeters

BS base station

CMOS complementary metal oxide semiconductor

D deliverable DC direct current

DAC digital to analog converter

dB decibel

dBm power in decibels referenced to one milli-watt DUPLO full-duplex radios for local access project

DUT device under test electrical balance

EBD electrical balance duplexer

EMX electromagnetic simulator

EVM error vector magnitude

FD full-duplex

FDD frequency division duplex

FET field effect transistor

FFT fast Fourier transform

GHz giga (10<sup>9</sup>) Herz

GND ground

HR high resistive

IBFD in-band full-duplex

IBM international business machines corporation.

IC integrated circuit

IEEE institute of Electrical and Electronics Engineers

I/O input/output ISOL Isolation

IIP3 third-order interception point

IM intermodulation

IM1 first order intermodulation productIM3 third order intermodulation productISM industrial, scientific and medical

LNA low noise amplifier

DUPLO WP2 D2.2 7 / 76

#### **PROJECT DUPLO**

LO local oscillator

LSB least significant bit

LTE long term evolution

mA milli Ampere

MHz mega (10<sup>6</sup>) Hertz

MIMO multiple input multiple output

Mm millimeter

MOS metal oxide semiconductor

MSB most significant bit

mS milli Siemens

nH nano Henry

NoC network on chip

ns nano seconds

OFDM orthogonal frequency-division multiplexing

PA power amplifier

PC personal computer

PCB printed circuit board

pF pico Farad

PIFA planar Inverted-F Antenna

PTx transmit power

Q quality R resistor

RF radio frequency

RX receiver

S.A. spectrum analyzer

SAW surface acoustic wave

SDR software defined radio

SI self-interference

SIC self-interference cancellation SMA sub-miniature version A

SNDR signal to noise and distortion ratio

SNR signal to noise ratio

SoC system on chip

SOI silicon on insulator

SOTA state of the art

STS short-training-sequence

SV small variation

TDD time division duplex

TX transmitter u micro

USB universal serial bus VGA variable gain control

VSWR voltage standing wave ratio

DUPLO WP2 D2.2 8 / 76

#### **PROJECT DUPLO**

W watt

WARP wireless open-access research

WIFI WLAN products that are based on the Institute of Electrical and Electronics Engineers

(IEEE) 802.11 standards

WLAN wireless local area network

WP work package

Zant antenna impedance

Zbal balance network impedance

DUPLO WP2 D2.2 9 / 76

## 1. INTRODUCTION

The DUPLO project aims to increase the spectral efficiency of wireless communication devices by investigating the full-duplex concept. This concept proposes concurrent transmission and reception on the same spectral resources, and thus theoretically doubling the spectral efficiency or enable new communication schemes as described in [4]. In practice, however, the benefits of full-duplex deployment rely on the availability of radio devices which support full-duplex operation. These radios are confronted with severe design challenges, namely:

- Isolation: to prevent the RF-signal generated by the local transmitter (TX) from leaking onto its own receiver (RX), where it causes self-interference.

- Cancellation: to subtract any remaining self-interference from the RX path using knowledge of the TX signal.

The DUPLO project identified and quantified the main design requirements over the targeted network types and scenarios , and gives a preliminary distribution of the technical requirements over the different building blocks [4]. For the WP2 activities, radio solutions are targeted which are commercially attractive in terms of form-factor, system integration, process technology and operation flexibility [3]. This target is different from the full-duplex radio solutions presented in literature which mainly rely on physical dimensions (i.e., antenna spacing) and require bulky components, hampering dense and cost-efficient integration. The WP2 objective is, however, contradicting with the self-interference problem which is easier to resolve with large form factor devices, circuits and antenna structures.

WP2 developed different techniques and prototype designs at the *antenna*, *RF circuitry* and *transceiver* level. Having self-interference isolation and cancellation at these levels is beneficial as it reduces the requirements on the transmitter dynamic range since all transmitter imperfections are included in the cancellation, and it reduces the requirements on the receiver dynamic range since the signal-to-interferer ratio is improved already before the LNA as discussed in [3]. The first results have been reported in the project deliverables D2.1 [1] and D2.3.1 [2], and have been published in JSAC [3]. These documents present a link budget calculation over realistic systems and scenarios, and report on the different design considerations, implementation topologies and initial measurements. Basically, D2.1 [1] describes three prototype designs which have been fabricated and measured:

- The antenna prototype, which is implemented as a dual-polarized microstrip patch antenna. The radiation polarization between transmission and reception is orthogonal to achieve an intrinsic isolation. D2.1 [1] describes the design considerations and optimizations, and illustrates both the simulated and measured antenna performance. The self-interference isolation robustness is also illustrated with objects in the direct surrounding of the antenna. More detailed results have been published in [5].

- The RF circuit transceiver, which acts as a duplexer and thus interconnects the RF transmitter and receiver ports with a single port antenna. This duplexer is implemented as an electrical balance circuit processed in plain CMOS technology. The functional circuit elements are an on-chip transformer, a tunable balance network and a basic LNA. The tunability of the balance network enables to match the antenna impedance over different operation conditions. D2.1 [1] describes the design considerations and optimizations, and illustrates the isolation, tuning capabilities, bandwidth and other relevant performance measures of the electrical balance duplexer. More detailed results have been published in [5].

- The active cancellation network, which connects the transmitter with the receiver path in the RF domain as close as possible to the dual-port antenna. This cancellation enables to add a modified copy of the transmitted signal to the receiver, thus enabling to cancel transmitted signals directly coupled to the receiver or to cancel the reflected signals due to near-field reflections. D2.1 [1]

DUPLO WP2 D2.2 10 / 76

describes the selected topology, design considerations and initial performance measurements in combination with the antenna prototype also presented in D2.1 [1].

The work presented in D2.3.1 [2] and the progress of the analog transceiver design is not described in this document; it will be captured in the future WP2 deliverable D2.3.2. However, the main design requirement to provide an isolation of minimally 50dB over 10MHz in the direct path and eventually to provide an additional self-interference rejection circuit to suppress the near-field reflections is considered for the designs described in this document.

This document reports the final results on the *antenna* and *RF circuitry* work performed within WP2, by continuing the results presented in D2.1 [1]. With respect to prototype design, the following activities will be described:

- A second antenna prototype has been designed, fabricated and measured. This prototype builds on similar topology as the first prototype and offers the same functionalities, but provides better performance (e.g. bandwidth) and is smaller in size. A parametric optimization methodology has been applied to set the design parameters of this second antenna prototype. The measurement results of the second prototype are reported in this document. This second prototype will be used for integration in the WP5 activities, and the measurements are shared with WP3 to validate the digital cancellation algorithms.

- Measurements in the first electrical balance duplexer (EBD) prototype indicated two main issues potentially hampering the exploitation for full-duplex operation. These issues are the limited bandwidth and the limited linearity of the balance network. These issues are described in this document and a second prototype has been designed and fabricated to investigate the capability to resolve these specific issues. To avoid the complexity overhead, this second prototype includes the balance network only, without the transformer. Therefore, this prototype does not have the duplexer functionality and cannot be used in WP5. The first EBD prototype will be used for integration in WP5. Extensive measurements on the first prototype by using the prototype platform described in [6] are shared with WP3 to validate the digital cancellation algorithms.

- The work on the active cancellation has been continued by optimizing the network topology. The performance of the active cancellation network has been verified in combination with the antenna prototype, as reported in this document. This combination will be used for integration in WP5.

Given the growth of interest in full-duplex and the increased number of publications proposing new radio techniques, this document also gives an overview of current state-of-the-art which apply similar antenna or circuit topologies. The WP2 work has been published on top-tier and well-selected conferences and journals; the main accepted publications up to now are listed in chapter 6.

DUPLO WP2 D2.2 11 / 76

#### 2. FULL-DUPLEX TECHNOLOGY AT ANTENNA-LEVEL

#### 2.1. Introduction on antenna techniques

At antenna level, the DUPLO project focuses on the research of new antenna SI suppression techniques implementable in compact form-factor devices, which means that traditional antenna separation techniques thoroughly studied in literature ([7, 8, 9, 10, 11]) must be replaced by other antenna structures which allow efficient integration.

This document reports the optimization process of the full-duplex antenna solution which is described in detail in the previous deliverable D2.1 [1]. The design of the second antenna prototype is extensively described as well as its manufacturing and evaluation.

### 2.1.1. Overview of the proposed solution

From the antenna point of view, to minimize the RF self-interference in a reduced area is really challenging since both requirements are rather contradicting at antenna level. However, the DUPLO project has developed a single-antenna solution which offers high isolation between the ports in a reduced size, suitable for compact form-factor devices such as small-cell access points. The proposed solution makes use of antenna polarization to prevent full-duplex self-interference. The polarization of an antenna dictates the direction and sense of the electric field vector. The maximum energy transferred between two electromagnetical waves will only occur if both waves have the same polarization. Contrarily, the transferred energy between orthogonal polarizations is zero. Considering this fact, full-duplex antennas can use orthogonal polarization for transmission and reception purposes to minimize the self-interference from the TX to the RX [1, 5].

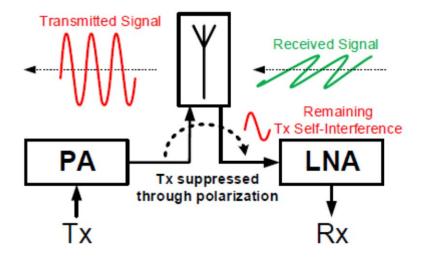

Orthogonal polarizations can be generated over the same radiating aperture using dual-polarized antennas, which consist of single radiating elements capable of generating orthogonal polarization using two independent excitation ports. Dual-polarized antennas have been widely applied in conventional wireless communication systems. Besides the ability to improve the overall system performance by means of polarization diversity, they are also able to provide double transmission channels in a frequency-reuse system. In the case of full-duplex scenario, the two antenna ports are connected to the RX and TX respectively as FIGURE 1 shows. The antenna isolation will determine the self-interference that leaks into the reception chain.

**FIGURE 1.** Dual-polarized antenna operation in full-duplex applications.

DUPLO WP2 D2.2 12 / 76

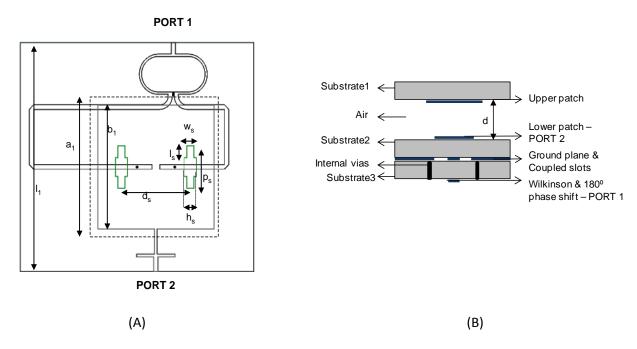

The dual-polarized antenna developed within DUPLO project has been implemented with microstrip technology because of its properties to enable low profile, low cost design and easy integration with the others RF components. For a microstrip patch antenna, dual linearly-polarized operation can be obtained by using a pair of probe feeds to respectively excite two orthogonal fundamental modes from a single radiating patch, however some undesirable higher-order modes would be also stimulated causing cross-polarization radiation, and the discrimination between the two polarizations is therefore degraded. With the aim of suppressing the cross-polarization at each feeding port of the dual-polarized microstrip antenna, and thus improving the isolation level between ports, the antenna structure incorporates different excitation techniques as FIGURE 2(A) shows. In particular, the antenna is symmetrically excited by a dual-feed system with a phase difference of 180º in order to minimize the appearance of higher-order modes. Additionally, the feed structure also includes a pair of coupling slots, in order to increase the isolation between both excitation ports. As can be seen from FIGURE 2(B), the antenna geometry consists of two stacked patches excited by means of a slot-coupled dual-feed network and a microstrip line. The antenna is composed of three dielectric substrate layers (with the same dielectric constant and thickness) and one air layer which separates the two patches. PORT 1 excites the antenna by means of a Wilkinson power divider, a half-wavelength delay line and two coupled-slots. Moreover, one microstrip line with matching stubs for  $50\Omega$  impedance matching is used for antenna excitation at PORT 2. Through this geometry, PORT 1 and PORT 2 excite linear polarization in the horizontal and vertical planes respectively.

**FIGURE 2.** Structure of the stacked-patch dual-polarized antenna. (A) Top view of the antenna, (B) multilayer antenna stack-up.

DUPLO WP2 D2.2 13 / 76

## 2.1.2. Evaluation of the first DUPLO antenna prototype

The antenna structure described in previous section was designed and manufactured using Roger substrate with 3.55 dielectric constant and a 0.508mm thickness, resulting in a 90x90mm square antenna area. FIGURE 3 shows a picture of the dual-polarized antenna first prototype.

FIGURE 3. Final dual-polarized antenna with SMA connectors.

The antenna performance in terms of impedance matching, isolation and radiation properties was experimentally evaluated. TABLE 1 summarizes the main technical specifications of the antenna. The isolation between ports is 50dB over a wide bandwidth (>100MHz), in 90x90mm square area, which allows the employment of this antenna in compact form factor solutions, e.g. small cell access points. The antenna also provides good cross-polar discrimination: more than 20dB within the 3dB antenna beam-width (60 degrees). However, the antenna performance is limited in bandwidth (BW) by the antenna impedance matching. The return loss (for both antenna ports) is below -10dB for 10MHz BW.

**TABLE 1.** Specification of the dual-polarized antenna.

| Specification       | Value    | Unit    |

|---------------------|----------|---------|

| Operation frequency | 2.45     | GHz     |

| Antenna Isolation   | >50      | dB      |

| Return loss         | <-10     | dB      |

| SIC bandwidth       | 100      | MHz     |

| Matching bandwidth  | 10       | MHz     |

| Cross-polarization  | >20      | dB      |

| 3dB beam-width      | >60      | Degrees |

| Antenna Size        | 90x90x11 | mm      |

DUPLO WP2 D2.2 14 / 76

The DUPLO project has selected 2.45GHz as the central frequency and a signal bandwidth of 10MHz for demonstration [12]. Therefore, this dual-polarized antenna prototype fully satisfies the technical requirements for the DUPLO proof-of-concept and is suitable for the integrated demonstrator. However, the reduced operational bandwidth (limited by the impedance matching) limits the capacity of the full-duplex link. This bandwidth limitation opens the door for antenna improvement with the aim of making it compatible with currently used wireless standards, e.g. WiFi standard from 2.4GHz to 2.48GHz. Consequently, based on the optimization of the results obtained from first antenna prototype introduced in deliverable D2.1, a second antenna prototype has been designed. The optimization process focused on the increment of the antenna bandwidth while maintaining the current performance in terms of antenna isolation. Additionally, the reduction of the antenna size was also objected during this optimization. The antenna structure proposed in D2.1 has been optimized and new excitation topologies have been explored to achieve the new technical requirements depicted in TABLE 2.

| 7.1022 21 Footimodi targoto for addi polarizoa amorina optimization. |                                              |  |

|----------------------------------------------------------------------|----------------------------------------------|--|

| Specification                                                        | Value                                        |  |

| Operation frequency                                                  | WiFi band 2.4-2.48 GHz                       |  |

| Antenna Isolation                                                    | >50                                          |  |

| Return loss                                                          | <-10                                         |  |

| Cross-polarization                                                   | >20                                          |  |

| 3dB beam-width                                                       | >60                                          |  |

| Antenna size                                                         | Reduction of radiating area in more than 30% |  |

**TABLE 2.** Technical targets for dual-polarized antenna optimization.

#### 2.2. Second dual-polarized antenna prototype

#### 2.2.1. Dual-polarized antenna design details

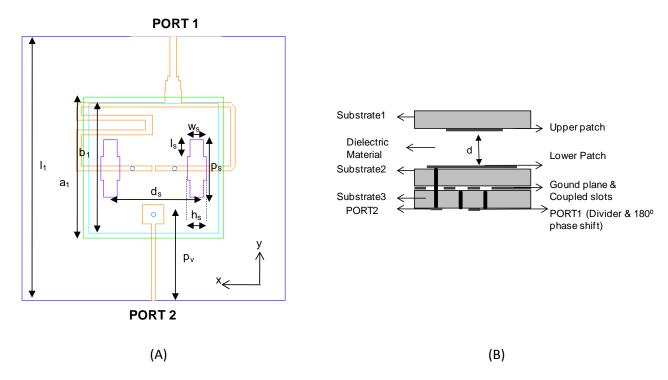

As mentioned in previous section, the structure of the dual-polarized antenna first prototype has been modified in order to reach more challenging requirements. The DUPLO project mainly targets solutions for wireless radios to make possible full-duplex operation in compact form factor devices, therefore the reduction of the size of the developed solutions is crucial. Considering the antenna geometry showed in FIGURE 2, the dual-polarized antenna size is mainly limited by the excitation networks used for the generation of highlyisolated dual-orthogonal polarizations. To overcome this size limitation, the feeding networks of both ports have been replaced by more compact solutions. Firstly, PORT 1 is excited by 180º phase shifted lines combined by a Wilkinson divider which use a lot of space on the bottom of the substrate 3. This feeding network has been replaced by a 1:2 divider and a meander line which introduces 180º phase shift between the divider branches, as FIGURE 4 illustrates. By doing so, the signals have equal amplitudes and 180º phase difference when they arrive to the coupled-slots. Consequently, the x-directed polarization mode is symmetrically excited through PORT 1, and the higher-order modes are suppressed. Secondly, in the first dual-polarized antenna model, PORT 2 is excited by a microstrip line including  $50\Omega$  matching stubs, imposing to lengthen the size of the overall antenna along the y-axis. However, the use of an internal via would provide some extra area to host the microstrip line, while the position of this internal via with respect to the excitation patch can be used to tune the  $50\Omega$  matching of PORT 2. By doing so, the size of the dual-polarized antenna can be reduced by 30%, resulting in an overall dimension of 60x60mm. The new dual-polarized antenna geometry is given in FIGURE 4(A) where both new feeding networks for respectively PORT1 and PORT2 are shown.

DUPLO WP2 D2.2 15 / 76

**FIGURE 4.** Geometry of the new dual-polarized antenna including modifications to PORT1 and PORT2 excitation networks. (A) Top view of the antenna, (B) multilayer antenna stack-up.

The antenna stack-up of the new dual-polarized antenna model (FIGURE 4(B)) is similar to the stack-up of the first prototype. The antenna consists of three dielectric substrate layers with the same thickness and dielectric constant. The upper patch is placed on the bottom of substrate 1, while lower patch is placed on the top of substrate 2. The coupled slots are printed of the back of substrate 3, while the new feeding lines are placed on the top of this substrate. The main difference between both antenna stack-ups lies on the layer that separates both patches. In the first dual-polarized antenna prototype, the patches were separated by an air layer, however, in this second antenna model, the patches are separated by means of using a rigid dielectric material with a dielectric constant of 2.5. This allows to slightly reduce the distance between patches and consequently the overall antenna height decreases. Moreover, the insertion of this dielectric layer gives more robustness to the overall antenna structure. Finally this new stack-up, together with the new feeding networks previously described, increase the antenna bandwidth as shown later.

The optimum performance of the proposed antenna has been achieved by means of the parametric studies carried out on the full 3D electromagnetic model of the antenna. The sensitivity analysis of the proposed antenna with respect to its resonance frequency, impedance matching and antenna isolation as a function of each geometrical parameter is represented in TABLE 3. The simulations have been developed using Rogers substrate with 3.55 dielectric constant and a 0.508 thickness, while the patches are separated with a rigid material with a dielectric constant of 2.5. From this parametric study, it is concluded that the shapes of coupled slots has a strong effect on the isolation between antenna ports and the matching performance of PORT 1. On the contrary, the matching of PORT 2 is more sensitive to the distance and size of radiating patches as well as the position of the internal via used for PORT 2 excitation.

DUPLO WP2 D2.2 16 / 76

**TABLE 3.** Parametric studies of the proposed antenna with respect to its resonance frequency, impedance matching and antenna isolation as a function of the design geometrical parameters. (SV - small variation)

| Geometrical Parameter                                        | Resonance<br>frequency   | Impedance<br>Matching      | Antenna Isolation |

|--------------------------------------------------------------|--------------------------|----------------------------|-------------------|

| Length of upper patch (a₁ ↑)                                 | <b>\</b>                 | <b>\</b>                   | SV                |

| Length of lower patch (b₁↑)                                  | <b>\</b>                 | <b>\</b>                   | SV                |

| Distance between coupled slots (d₅↑)                         | PORT 1 -↓<br>PORT 2 - SV | PORT 1 -↓<br>PORT 2 - SV   | SV                |

| Length of coupled slots (p₅个)                                | PORT 1 -个<br>PORT 2 - SV | PORT 1 - SV<br>PORT 2 - SV | <b>\</b>          |

| Width of coupled slots (h₅↑)                                 | PORT 1 -个<br>PORT 2 - SV | PORT 1 - ↓<br>PORT 2 - SV  | <b>\</b>          |

| Length of coupled slots- upper/lower part (l₅个)              | PORT 1 -个<br>PORT 2 -SV  | PORT 1 - 个<br>PORT 2 - SV  | <b>↓</b>          |

| Width of upper part of coupled slots- upper/lower part (w₅↑) | PORT 1 - ↓<br>PORT 2 -SV | PORT 1 - SV<br>PORT 2 - SV | <b>\</b>          |

| Position of the internal via - PORT2 (p <sub>v</sub> ↑)      | PORT 1 -SV<br>PORT 2 - ↓ | PORT 1 -SV<br>PORT 2 - ↓   | SV                |

| Distance between patches (d个)                                | <b>+</b>                 | <b>+</b>                   | SV                |

The optimization of the geometrical antenna parameters has been carried out defining an input impedance matching better than -10dB and an isolation better that -50dB as target objectives. Additionally, the Trust Region Framework algorithm has been used for the parametrical optimization. This algorithm is a local optimizer which builds a linear model on primary data in a region around the starting point. Then, the modeled solution is used as new starting point until it converges to an accurate model of the data. In the case of the proposed new dual-polarized antenna structure, this algorithm takes the advantage of input impedance matching and antenna isolation sensitivity to reduce the number of simulations needed and thus speed up the process of optimization [13]. The optimum dimensions obtained from this parametrical optimization are depicted in TABLE 4.

DUPLO WP2 D2.2 17 / 76

**TABLE 4.** Dual-polarized antenna design parameters.

| Geometrical Antenna Parameter | Value |

|-------------------------------|-------|

| d[mm]                         | 6.97  |

| I <sub>1</sub> [mm]           | 60.00 |

| a <sub>1</sub> [mm]           | 33.07 |

| b <sub>1</sub> [mm]           | 30.43 |

| d <sub>s</sub> [mm]           | 20.34 |

| ps [mm]                       | 13.73 |

| I <sub>s</sub> [mm]           | 3.96  |

| h <sub>s</sub> [mm]           | 2.47  |

| w <sub>s</sub> [mm]           | 3.16  |

| p <sub>v</sub> [mm]           | 20.2  |

The simulation results considering these geometrical values are presented in FIGURE 5(A) and FIGURE 5(B) respectively. These simulation results show an isolation between ports better than 50dB over the full antenna impedance bandwidth, while the antenna impedance is better than -10dB in more than 70MHz BW.

**FIGURE 5.** Simulated results for the optimized dual-polarized antenna. (A) Return Loss, (B) isolation between antenna ports.

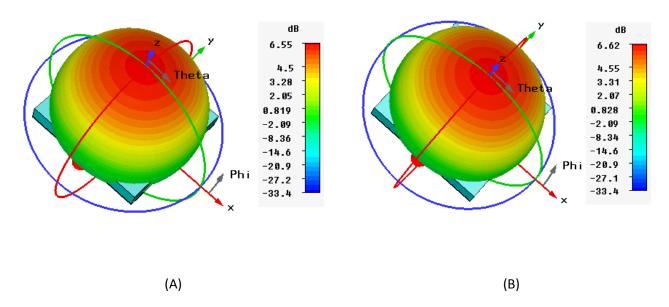

FIGURE 6(A) and FIGURE 6(B) show the 3D radiation patterns for horizontal and vertical polarizations respectively at 2.45GHz. These figures illustrates that both orthogonal polarizations presents similar antenna gain.

DUPLO WP2 D2.2 18 / 76

**FIGURE 6.** Simulated Radiation pattern results for the dual-polarized antenna at 2.45GHz. (A) Horizontal polarization, (B) vertical polarization.

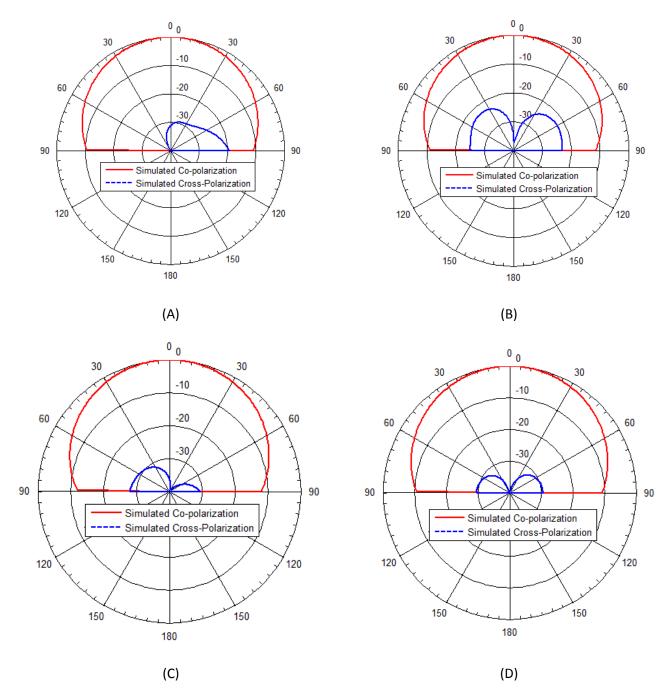

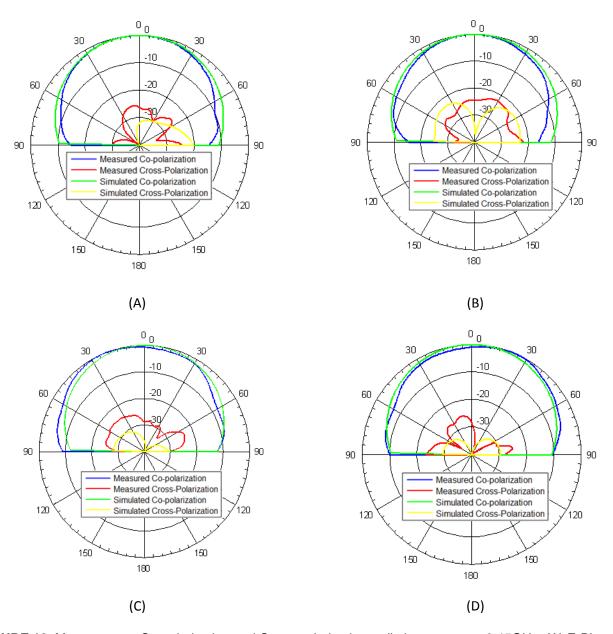

FIGURE 7 shows the two-dimensional radiation patterns for the new antenna structure in the two principal planes. From the obtained results, it is interesting to highlight that the antenna provides a broad coverage area with a 3dB antenna beamwidth wider than 70 degrees, while the cross-polarization level is less than - 20dB within the 3dB beamwidth in the two principal radiation planes.

DUPLO WP2 D2.2 19 / 76

**FIGURE 7.** Simulated co-polarization and cross-polarization radiation patterns at 2.45 GHz. (A) E-plane for PORT 1, (B) H-plane for PORT 1, (C) E-plane for PORT 2, (D) H-plane for PORT 2.

DUPLO WP2 D2.2 20 / 76

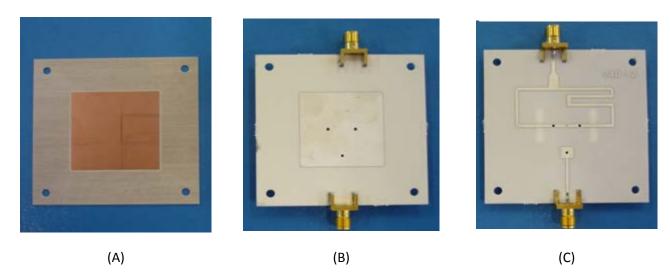

## 2.2.1. Second prototype implementation and evaluation

The new antenna model has been manufactured with the aim of validating the performance of the new antenna structure. FIGURE 8 shows the different PCB's that integrate the overall dual-polarized antenna. The upper PCB, showed in FIGURE 8(A), contains the upper patch. The lower PCB contains the lower patch (printed on the top of the PCB), the feeding networks (printed on the bottom of the PCB), as well as the coupled slots and internal vias for antenna excitation. The top and bottom sides of lower PCB are shown in FIGURE 8(B) and FIGURE 8(C) respectively.

**FIGURE 8.** Manufactured PCB's for dual-polarized antenna. (A) Upper patch., (B) lower patch, (C) feeding networks for PORT 1 and PORT 2.

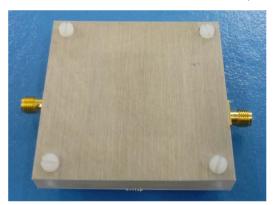

FIGURE 9 shows the integrated prototype of the new dual-polarized antenna model. The two independent PCB's are stacked together with the rigid dielectric material layer and four nylon screws which ensure the physical contact among the different layers of the antenna (similar antenna performance has been obtained when metallic screws are used instead of nylon screws). Two SMA connectors are used for the interfaces of PORT 1 and PORT 2. This RF interfaces will be connected to the TX and RX paths of the full-duplex transceiver.

FIGURE 9. New dual-polarized antenna prototype.

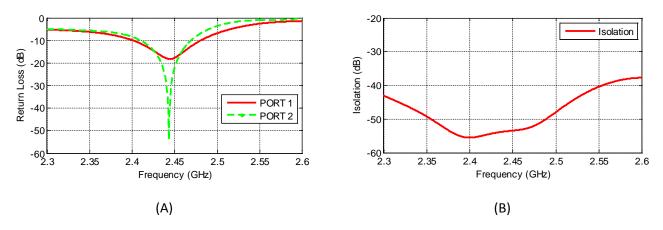

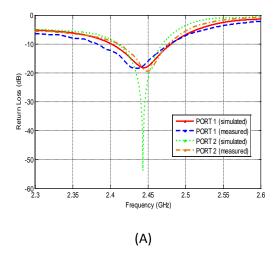

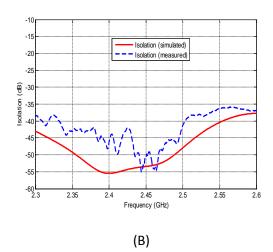

The dual-polarized antenna performance in terms of matching and isolation has been evaluated by connecting the antenna ports to a network analyzer configured to record S-parameters (the antenna was placed in the laboratory on a non-controlled environment). FIGURE 10(A) shows the measured antenna matching while FIGURE 10(B) depicts the measured isolation between ports. The measurement results indicate a good agreement between simulations and measurements. Both antenna ports provide good matching at 2.45 GHz while the impedance bandwidth is around 70MHz. The isolation level between the two feeding ports is

DUPLO WP2 D2.2 21 / 76

illustrated in FIGURE 10(B). It shows and isolation of more than 43dB over the entire antenna impedance bandwidth. The difference between the measurements and simulations is due to low signal level measured as well as some dissimilarities between simulated model and constructed prototype. Moreover, environmental reflections can also cause the variations observed between simulation and measurement results.

**FIGURE 10.** Measurement results of the dual-polarized antenna. (A) Impedance matching results of PORT 1 and PORT 2, (B) isolation between antenna ports.

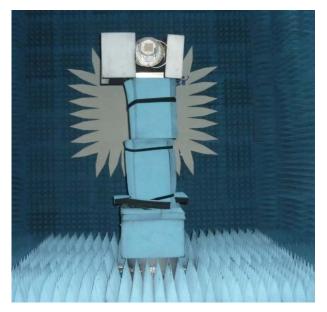

Since the two excitation ports are well decoupled, low cross-polarization radiation is expected at each antenna port. The radiation patterns of the second antenna prototype have been measured inside the anechoic chamber, as depicted in FIGURE 11. The measured radiation patterns at 2.45GHz are shown in FIGURE 12; this figure illustrates the radiation patterns for PORT 1 and PORT 2 in the two principal planes. For PORT 1, the cross polarization level is -27dB in the E-plane and -22dB in the H-plane, while for PORT 2, the cross polarization level is -25dB in the E-plane and -26dB in the H-plane. The 3dB antenna beamwidth is around 70 degrees for both orthogonal polarizations.

**FIGURE 11.** Dual-polarized antenna placed on the positioner system of the anechoic chamber.

DUPLO WP2 D2.2 22 / 76

**FIGURE 12.** Measurement Co-polarization and Cross-polarization radiation pattern at 2.45GHz. (A) E-Plane for PORT 1, (B) H-plane for PORT 1, (C) E-plane for PORT 2, (D) H-Plane for PORT 2.

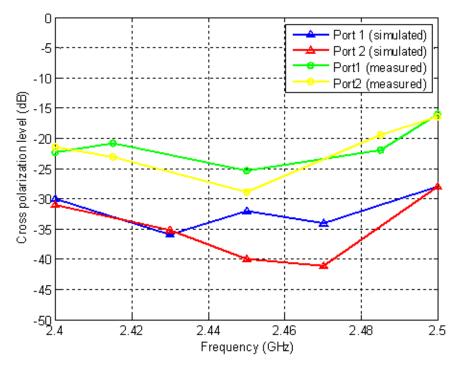

As can be seen from FIGURE 10, the isolation between ports worsens at the edges of the 2.4-2.5GHz band, providing better performance at the center of the band. This increment in the coupling between feeding ports can cause the degradation of the cross-polarization level. In order to evaluate the impact of ports coupling, the cross-polarization level at broadside direction over the 2.4-2.5GHz frequency band has been evaluated. FIGURE 13 depicts the obtained results for both antenna feeding ports. These results indicate similarity in the trend for both measured and simulated cross polarization level. The cross polarization keeps below -20dB over the full WiFi band from 2.4 GHz to 2.48 GHz, and only a minor increment is observed above 2.48GHz.

DUPLO WP2 D2.2 23 / 76

**FIGURE 13.** Dual-polarized antenna cross polarization level from 2.4 GHz to 2.5 GHz.

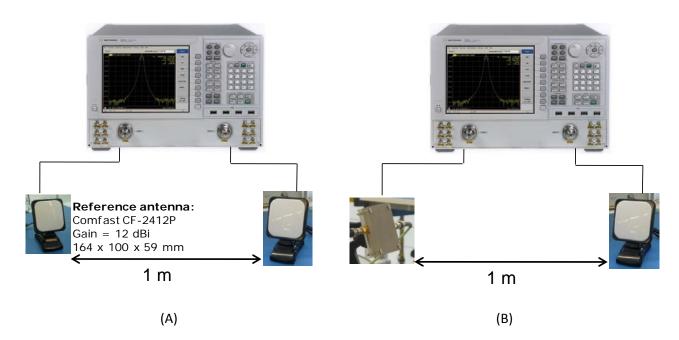

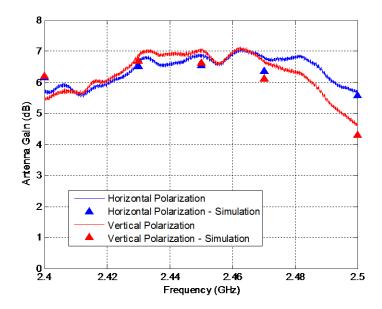

The gain of the antenna has been also characterized by means of experimental tests in the laboratory and in the anechoic chamber. The gain measurement consists of two steps as shown in FIGURE 14. Firstly, two reference antennas are connected to a network analyzer configured to measure S-parameters. The reference antennas are directive antennas with 12dB of antenna gain and 164x100x59mm size operating in the 2.4-2.5GHz frequency band. The antennas are placed in a point-to-point link respecting the far-field region condition (FIGURE 14(A)). Secondly, one of the reference antennas is replaced by the dual-polarized antenna, maintaining the same distance (FIGURE 14(B)). Finally, by comparing the S21 parameter of both measurement setups (taking into account the gain of the reference antenna), the gain of the dual-polarized antenna is calculated: FIGURE 15 shows the calculated antenna gain for both vertical and horizontal polarizations. These results show that the antenna gain is almost 7dB for both ports at 2.45GHz. A degradation of the antenna gain is observed at the edges of the band due mainly to the antenna mismatch at these frequency points. The antenna gain was also measured inside the anechoic chamber at the frequency of 2.45GHz. The deviations of the obtained results were negligible with respect to the gain measurements obtained in the laboratory at this frequency.

DUPLO WP2 D2.2 24 / 76

**FIGURE 14.** Antenna gain measurement setup. (A) Setup 1 - Two reference antennas in a point-to-point link, (B) Setup 2 - One reference antenna and dual-polarized antenna in a point-to-point link.

FIGURE 15. Measured gain of the dual-polarized antenna for vertical and horizontal polarizations.

DUPLO WP2 D2.2 25 / 76

## 2.2.2. Performance evaluation of the second antenna prototype

TABLE 5 outlines the measured technical specifications of the new dual-polarized antenna considering two different operational bandwidths. As previously indicated, the signal BW selected for DUPLO demonstrator is 10MHz BW. Considering this operational bandwidth, the new implemented prototype provides self-interference isolation better than -49dB with an input return loss better than -15dB. The antenna gain and cross-polarization discrimination are 6.5 and 24dB respectively, while the antenna efficiency is 75%.

The new dual polarized antenna can operate over wider bandwidths with a minor degradation of antenna performance. In particular, the antenna isolation decreases only 7dB when a WiFi band is considered, while the input return loss is slightly worse than target specification. Cross polar discrimination remains better than 20dB while the antenna efficiency in this frequency band is 70%.

**TABLE 5.** Summary of technical specification for second dual-polarized antenna prototype.

| DUPLO demonstrator BW = 10 MHz                  | WiFi band 2.4 - 2.48 GHz    |  |

|-------------------------------------------------|-----------------------------|--|

| Antenna Size: 60 x 60 x 8 mm                    |                             |  |

| Dual linear polarized antenna: V/H polarization |                             |  |

| RF interface : SMA connector                    |                             |  |

| Antenna Return loss < -15 dB                    | Antenna Return loss < -9 dB |  |

| Antenna Isolation < -49 dB                      | Antenna Isolation < - 42 dB |  |

| Antenna Gain > 6.5 dB                           | Antenna Gain > 5.5 dB       |  |

| Antenna XPD > 24 dB                             | Antenna XPD > 20 dB         |  |

| 3dB BeamWidth > 70º                             | 3 dB BeamWidth > 75º        |  |

| Antenna efficiency > 75%                        | Antenna efficiency > 70%    |  |

The optimization of the antenna radiating structure has achieved to increase the operating bandwidth at the same time so that antenna radiating area have been reduced by 50%, as can be seen from TABLE 6. This new prototype is being integrated in the DUPLO demonstrator.

**TABLE 6.** Comparative between manufactured dual-polarized antenna prototypes.

|                     | First antenna prototype | Second antenna prototype |

|---------------------|-------------------------|--------------------------|

| Antenna Size        | 90 x 90 x 11 mm         | 60 x 60 x 8 mm           |

| Polarization        | Dual linear V/H         | Dual linear V/H          |

| RF Interface        | SMA connector           | SMA connector            |

| Antenna Return loss | < -10 dB in 10 MHz BW   | < -10 dB in 70 MHz BW    |

| Antenna Isolation   | < - 46 dB in 70 MHz dB  | < -42 in 70 MHz BW       |

DUPLO WP2 D2.2 26 / 76

#### 3. FULL-DUPLEX TECHNOLOGY AT RF CIRCUIT LEVEL

With the 180nm CMOS prototype [5] this work package managed to demonstrate the feasibility of using electrical balance duplexers to cancel self-interference at the direct RF interface between the antenna and the transceiver. In this chapter, we will briefly explain the operation of the EBD and discuss the target specifications. Then, a new prototype chip which was fabricated and tested in order to combat some of the remaining limitations of the first prototype is presented.

#### 3.1. The electrical-balance duplexer concept and target specifications

In full duplex operation, concurrent TX and RX operation at the same frequency is required. Recently, the use of hybrid transformers to achieve signal cancellation based on electrical balance (EB) has been proposed to achieve tunable duplexer filters for FDD [14, 15, 16]. In task 2.2, this technique is applied in the context of full duplex, where it shows to provide RF self-interference cancellation for compact radio devices [3, 5, 1].

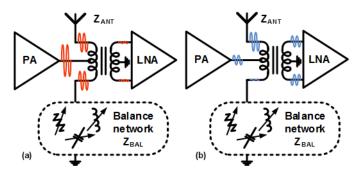

FIGURE 16 shows the conceptual operation of an EB duplexer, comprising a hybrid transformer and a so-called balance network, which is essentially a tunable dummy load impedance.

**FIGURE 16.** Electrical balance operating principle for (a) TX operation and (b) RX operation: in FD, (a) and (b) occur at the same time and frequency.

Ideally, the transmitter signal (output of the PA) splits up exactly between the antenna and the balance network, so that no differential voltage excitation occurs and the hybrid transformer essentially subtracts the voltage across these impedances. This so-called "electrical balance condition" is limited by the accuracy with which the balance network impedance ( $Z_{BAL}$ ) can mimic antenna impedance ( $Z_{ANT}$ ). By tuning the resistance and reactance of balance network independently with high precision, >50dB of self-interference cancellation (SIC) can be achieved across the channel bandwidth (BW) [14]. By virtue of this purely passive cancellation process, any noise and nonlinearity products generated in the transmitter are also cancelled in such electrical balance condition.

The principle of electrical balance is applicable to both FDD and FD: the TX to Z<sub>ANT</sub> path as well as the Z<sub>ANT</sub> to RX path have a wideband transformer response, while the TX to RX cancellation is required at both the TX and RX frequencies simultaneously (FDD) [15] or at a single frequency only (FD).

In our previous work [3], [1], we have proposed the usage of an EBD to enable self-interference cancellation in RF for FD operation, and its potential has been validated based on real measurements with on a prototype [5]. This prototype has been integrated in a test and validation radio platform, and an intelligent tuning algorithm has been developed. This work has been published [6] and is considered as part of the DUPLO WP5 activities.

DUPLO WP2 D2.2 27 / 76

## 3.1.1. Limitations of the first prototype

There are a number of important limitations in the prototype presented in D2.1 [1] and in [3, 5]. These are:

- The 50dB isolation bandwidth of the prototype is limited to about 6 to 10MHz, which is limiting the applicability in high data-rate communication applications. This limitation mainly arises from the fact that the impedance variation across frequency of the antenna is much larger than the variation across frequency of the balance network impedance.

- The linearity of the balance network limits the TX path IIP3 of the prototype to 20 to 38dBm. This means that IM-products arising at the Rx input will exceed the level of the direct leakage from about >-5dBm TX power.

#### 3.1.1.1. Limited bandwidth

During the design of the first prototype, the key innovation target was to create the capability of providing electrical balance with a real antenna. In order to have a design that would do that, with some certainty, the balance network was designed considering a realistic antenna and antenna interconnection. Very little design effort was attributed to the frequency variation robustness of the electrical balance condition; as such the design approach was to achieve best-as-possible bandwidth for a single-frequency balance condition.

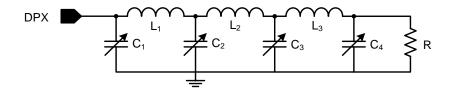

In order to significantly advance the state-of-the-art in terms of bandwidth, an alternative design is required. Instead of a the simple resistor-capacitance (R-C) type network, where imaginary and real impedance are orthogonally tuned, a balance network with more tuning capability is required. Such higher tuning freedom across frequency implies a balance network that is

- higher-dimensional in nature, i.e. more than just a R and C that may be tuned;

- tuned in an orthogonal manner for all tuning dimensions, in order to be able to adjust both real and imaginary, independently, with the goal of tuning the impedance across frequency.

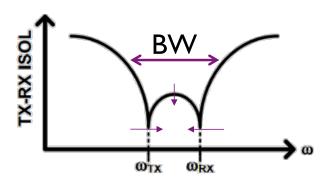

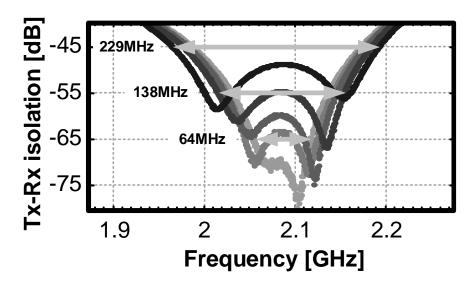

The isolation of such a network is shown in FIGURE 17, where it is clear that BW can be traded off for isolation if two individual notches can be tuned. This is proposed in [16] for achieving concurrent isolation at two frequency points (TX and RX frequencies in a FDD-type system). Other work, albeit in the FDD context, also implements this idea to achieve >40dB isolation for <160MHz of bandwidth [5]. This technique can also be exploited in the frame of FD when, where the transmitted and received signal are equal and where the isolation bandwidth is limited.

FIGURE 17. Electrical balance across frequency: 'dual-notch' capabilities for larger bandwidth.

In our second prototype, we implemented this approach by increasing the amount of tuning dimensions to 4, where the first prototype only had 2 dimensions (R and C). The design of this second prototype is described in detail further in this document.

DUPLO WP2 D2.2 28 / 76

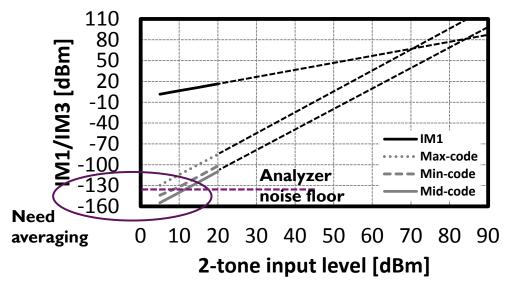

## 3.1.1.2. Linearity limitations and specifications

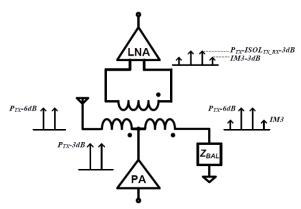

The first prototype also indicated that the EBD is subjected to linearity limitations in the balance network. The effect of such nonlinearity is illustrated in FIGURE 18 [15], where a 2-tone signal is transmitted through an EBD. In case of nonlinear distortion in the balance network, 3<sup>rd</sup> order intermodulation products are generated. As these distortive tones are not present at the antenna, they directly leak into the receiver (LNA input) . This will reduce the receiver sensitivity and potentially block the wanted received signal especially with multi-tone signals, causing intermodulation (IM) tones on the neighboring sub-carriers.

FIGURE 18. Nonlinearities generated in the balance network directly leak into the receiver.

For useful operation, the leakage due to nonlinear distortion of the balance network should be lower than the 'normal' EBD self-interference leakage. The relation between the IIP3 and the different EBD parameters is described in [15] and equals to:

$$IIP3_{BAL}(dBm) > P_{TX}(dBm) + \frac{1}{2}ISOL_{TX-RX}(dB) - 9dB$$

In case of FD operation, this equation enables to calculate the required linearity to achieve lower IM products than the total isolation in the FD chain (e.g. RF, digital, ...). For a transmit power of 27dBm and a total SIC of 10dB, the IIP3 requirement for the balance network can be calculated to be:

$$IIP3_{BAL}(dBm) > 27 + \frac{100}{2} - 9dB = 68$$

The obtained IIP3 requirement is extremely challenging; it typically compares to the linearity required of typical RF switch applications.

Reversing the procedure, the maximum transmit power can be calculated at which the first prototype can operate. Based on the measured performances of the first prototype, IIP3 = 20dBm and 50dB RF SIC, the maximum transmit power equals:

$$P_{TX}(dBm) < IIP3_{BAL}(dBm) - \frac{1}{2}ISOL_{TX-RX}(dB) + 9dB$$

=  $20 - \frac{50}{2} + 9 = 4$

DUPLO WP2 D2.2 29 / 76

This transmit power however assumes that digital cancellation will remove the EBD-induced IM3 products in the digital baseband. If however a 100dB isolation is required (e.g. 50 RF SIC and 50 dB digital SIC), without having to cancel EBD-induced nonlinearities, the maximum Tx power is limited to only:

$$P_{TX}(dBm) < IIP3_{BAL}(dBm) - \frac{1}{2}ISOL_{TX-RX}(dB) + 9dB$$

=  $20 - \frac{100}{2} + 9 = -21$

Based on the above derivations, to fully prove that these electrical-balance duplexers are feasible for standard link-budget FD, a very high linearity (>68dBm IIP3) balance network is required. This will be targeted in the second prototype.

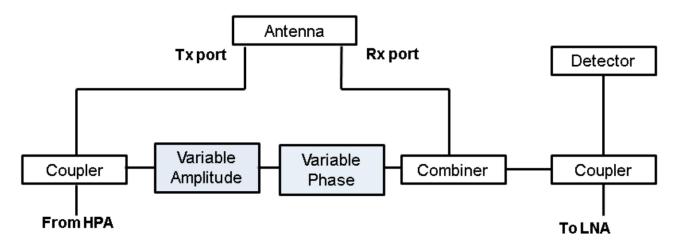

#### 3.1.2. Automatic tuning

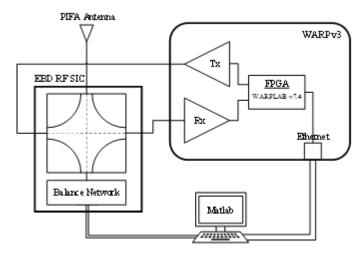

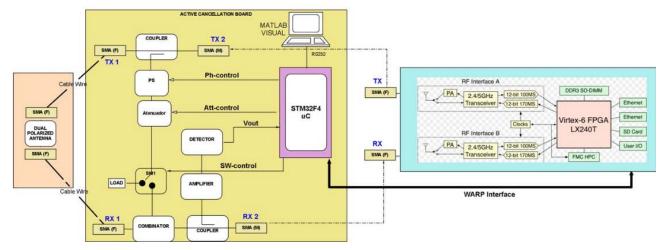

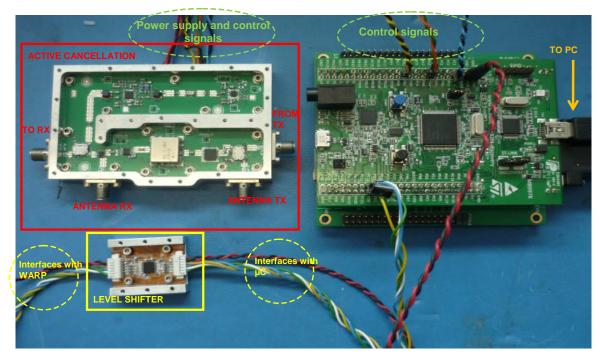

To ensure proper balancing conditions over different antenna operation conditions, the balance network of the EBD needs to be tuned to match the varying antenna impedance. An efficient tuning mechanism has been developed on a prototyping platform comprising the first EBD chip prototype, the WARPv3 platform and a commercial PIFA antenna [6]. This prototype platform is compliant with the integration activities in WP5, and therefore the tuning and the prototype platform will be discussed in detail in the D5.2. In this section, the tuning will be introduced briefly. The block diagram of the prototyping platform is given in FIGURE 19.

**FIGURE 19.** Prototyping platform including the first EBD chip prototype, WARPv3 and a single-port PIFA antenna.

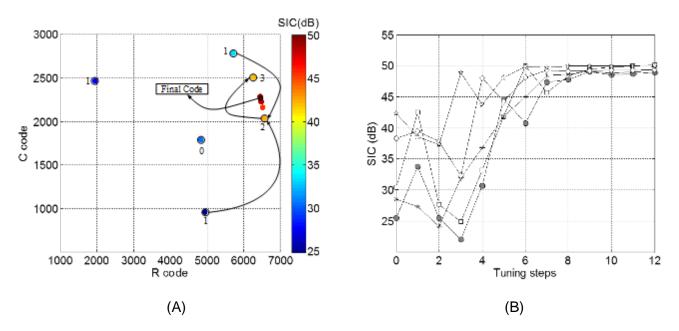

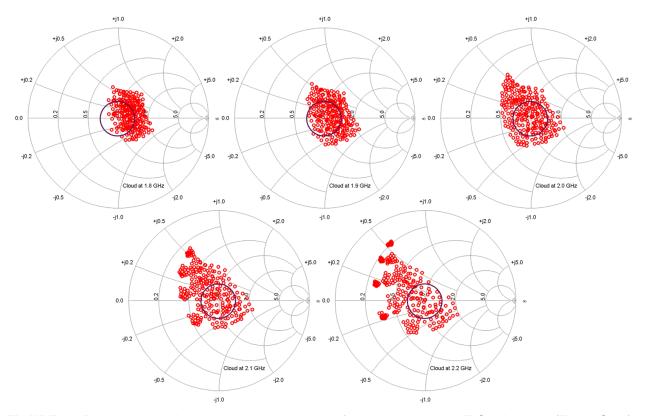

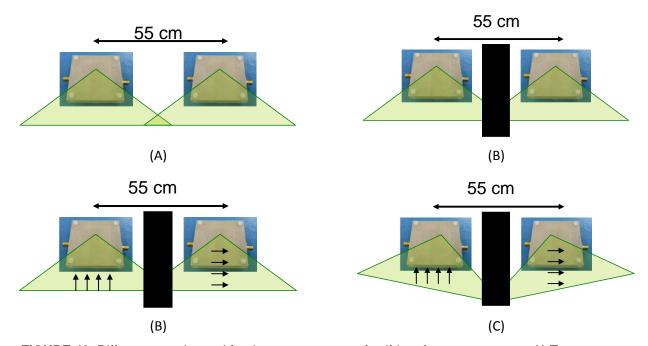

The tuning algorithm senses self-interference level and retunes the balance network if a certain threshold is exceeded (e.g. self-interference rejection <45dB). The tuning operates as an iterative process, and this process has been optimized to limit the amount of iterative steps and measurements. FIGURE 20 graphically illustrates the tuning algorithm in action. The left graph shows the different measurement points in the R/C plane, where the numbers indicate the tuning step. Based on the initial measurement point 0, the tuning algorithm determines 3 measurement points (indicated with '1') located at R/C values determined by the tuning algorithm. Based on the SIC values at these points, the algorithm calculates the R/C value for the next measurement point (indicated with '2'). This SIC value is compared with the surrounding values from the previous iteration etc. The graph on the right illustrates the SIC performance in function of the number of tuning steps over different antenna conditions. It is observed that after 10 iterations the targeted SIC is reached.

DUPLO WP2 D2.2 30 / 76

**FIGURE 20.** EBD tuning algorithm in action: (A) the iterative steps represented in the R/C plane and (B) the obtained SIC in function of the amount of tuning steps over different antenna conditions.

The tuning algorithm has been developed to operate on standard-compliant short-training-sequence (STS) symbols to enable tuning during normal transmission operation and to avoid ether pollution during tuning operation. More details will be given in D5.2.

#### 3.2. Second prototype: highly-linear, higher-dimensional balance network

## 3.2.1. Technology considerations: SOI CMOS versus bulk CMOS

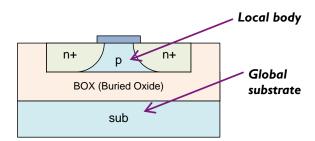

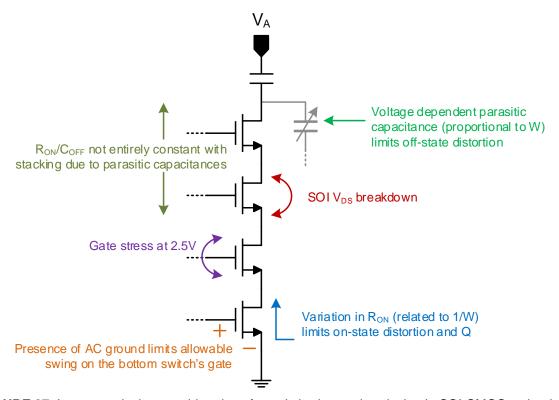

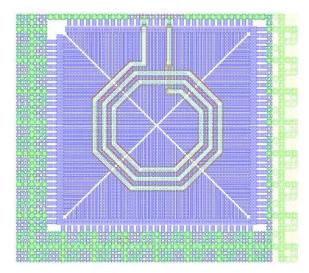

Silicon-on-Insulator (SOI) CMOS provides several advantages compared to bulk CMOS. It has a high-resistive (HR) substrate, which presents the opportunity to implement high-Q passives. Transistors implemented in this substrate have their own local body connection, implementing a true '3-terminal' transistor when left floating as shown in FIGURE 21.

FIGURE 21. SOI floating body devices.

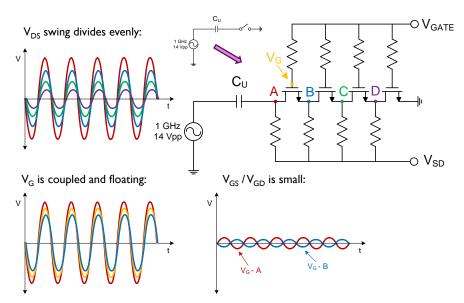

Thanks to the floating body, stacking multiple devices helps to reduce node-to-node stress when a large signal is applied, as illustrated for a switched capacitor unit cell in FIGURE 22.

DUPLO WP2 D2.2 31 / 76

FIGURE 22. Stacked switches in a switched capacitor implemented in SOI.

When the body voltage floats, no breakdown issues exist, because the gate and drain/source voltages are connected through a high resistor such that they are also floating (for AC signals, of course, for DC a bias level may still be applied to all nodes). Therefore the intrinsic parasitic capacitance of the device AC-couples the voltage swing and reduce the effective gate-source and gate-drain voltage ripple (as shown in the bottom of FIGURE 22). Because the junction diodes are much smaller compared to standard bulk CMOS, nonlinearity of the switches is also smaller, while allowing for a better R<sub>ON</sub>\*C<sub>OFF</sub> product and thus a larger tuning range.

Achieving high linearity (IIP3>68dB) in bulk CMOS leads to many design complications; prior work [17] has shown about 48dBm of IIP3 in CMOS, using down-conversion transformers. This IIP3 value however does not meet the targeted requirement, and the down-conversion transformers lead to additional design complications. Therefore, bulks CMOS might not be suited to design a highly linear balance network; SOI technology might be better suited, especially because an EBD is in essence a subset of RF switched components [18]. For all these abovementioned reasons, we designed the new balance network in silicon-on-insulator technology.

#### 3.2.2. Design considerations

#### 3.2.2.1. Topology comparison

The implementation of the balance network in SOI technology offers different topology options. In this section, different topologies are discussed.

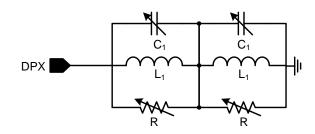

In [5], a simple R-C balance network topology similar to FIGURE 21 is used, with two tunable capacitors and two tunable resistors. This balance network topology is however not the optimal or SOI technology; switched capacitors in SOI can be implemented with very good on/off ratios and linearity, but tunable resistors are less affected by the benefits of SOI. Using only switched capacitors for tuning elements, the topology of FIGURE 21 logically transforms into something like FIGURE 22, while maintaining the amount of dimensions of tunability.

DUPLO WP2 D2.2 32 / 76

FIGURE 23. Equivalent balance network topology from [5].

**FIGURE 24.** Topology of FIGURE 3 transformed to use only tunable switched capacitors and maintain 4 tuning dimensions.

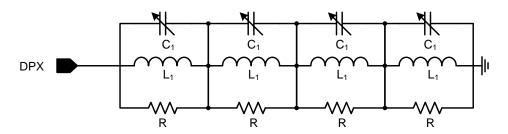

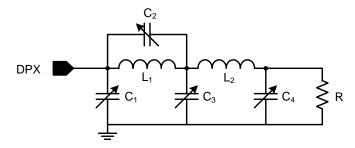

Although FIGURE 24 is a viable structure, it has a large layout area (four inductors) and it does not provide less trade-off between tuning range and linearity compared to other topologies. An alternative topology in this regard is shown in FIGURE 25. A differential version FIGURE 25 is presented in [15, 16] and uses transformers rather than inductors to gain additional benefit in a differential implementation. For a given tunable capacitor range, this approach can produce a larger impedance cloud than the topology in FIGURE 24. Furthermore, the number of inductors is reduced by one which is beneficial in terms of area.

FIGURE 25. A more optimal balance network topology.

Further investigation indicated that using at least one of the tunable shunt capacitors as a series tunable capacitance instead, as shown in FIGURE 26 offers several additional benefits: first, there are now only two inductors leading to area savings, and second, the series connected capacitor  $C_2$  can be viewed as a way to adjust the value of inductance  $L_1$ . This increases the orthogonality of the tunable components, and thereby improves the tuning freedom (at least for a single frequency).

DUPLO WP2 D2.2 33 / 76

FIGURE 26. Final topology as used in this design.

For this design project, design target equals a VSWR  $\approx 1.5$ , and a linearity >68dBm IIP3. We found that a tuning range of approximately 1pF each for  $C_1 - C_4$  will be sufficient for this and the topology of FIGURE 26 produces a good and fairly round impedance cloud when visualized on a Smith chart. Final top-level simulations of this design suggest that the simulated linearity from the balance network matches the system level specifications. Compared to the first prototype, this topology offers about twice as much tuning range.

## 3.2.2.2. Highly linear tuned capacitor design

Before looking at the particular implementation details of the tunable capacitor banks used in the balance network, it is useful to discuss the key design constraints that have motivated the design approach. These design constraints are graphically indicated in FIGURE 27.

FIGURE 27. Important design considerations for switched capacitor design in SOI CMOS technology.

DUPLO WP2 D2.2 34 / 76

The ultimate design goal of the balance network switched capacitor is to minimize its distortion, maximize its Ron/Coff, and to avoid over-stressing the devices. Some of the design tradeoffs that limit this goal are:

- In this SOI process, at least 4 devices need to be stacked to ensure stable off-state operation, and avoid drain-source voltage breakdown for 27dBm Tx power in the balance network.

- Ideally, transistor stacking can be done independent of  $R_{ON}/C_{OFF}$ . In reality, the parasitic capacitances present mean that  $R_{ON}/C_{OFF}$  degrades with more stacking.

- Due to voltage division from the parasitic capacitances present, voltage will not be divided evenly between all transistors in the stack. For relatively small unit cells used in a bank, this is be a bigger problem than in the case of a large RF switch. This requires a re-examination of the assumption that four stacked transistors are sufficient for the V<sub>DS</sub> breakdown issue. It also means that for this application there is little benefit in stacking more transistors than absolutely necessary.

- Most of the nodes in the switch stack can be given a DC bias to ensure that a large swing can be tolerated in the off-state without channel conduction (provided that there is sufficient AC coupling present). However, the source node of the bottom-most transistor in the stack is connected to an AC and DC short. The swing on the gate of this bottom transistor must therefore never exceed  $V_T$ .

- Sizing of the transistors is constrained by two opposing sources of non-linearity. In the off-state, non-linearity is generated by the voltage-dependent parasitic capacitances present in the switch layout. When the transistor width is increased, these parasitics increase, and linearity degrades. Therefore, the off-state operation prefers as small of switches as possible (but also with as good of AC coupling as possible). In the on-state, the non-linearity of the V<sub>DS</sub> / I<sub>DS</sub> transfer characteristic of the switches generates distortion. This signal-dependent channel resistance is reduced by increasing the width of the devices. Therefore, the on-state operation prefers large switches.

- For some specific width used, the distortion due to each effect is equal. Since extremely high Q is not necessary in the balance network design, in most cases we can simply find this particular width and accept the on-state/off-state Qs that result.

- Switch stacking in SOI only works under the assumption that the AC coupling of gate, source, drain, and bulk junctions is much stronger than the coupling of these terminals to ground via parasitics. In the design of a capacitor bank, where tunable elements must oftentimes be relatively small, but routing parasitics don't necessarily decrease accordingly, this is not always a valid assumption. If there is insufficient AC coupling, voltage will be unevenly divided across the switches in the stack, and the upper limit on how many switches can be stacked with any benefit is reduced. The important implication here is that if coupling is too weak, no amount of stacking will be able to provide enough voltage division to meet the V<sub>DS</sub> breakdown constraint a likely scenario for the LSB elements in our capacitor design.

DUPLO WP2 D2.2 35 / 76

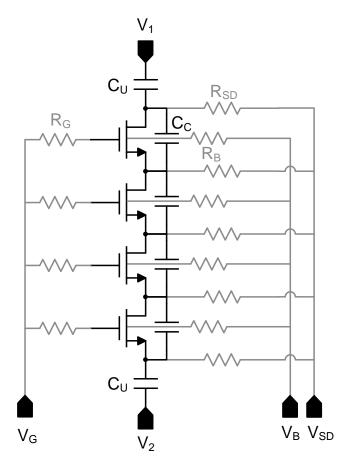

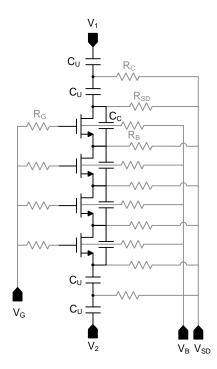

To address many of the design concerns discussed above, the switched capacitor structure of FIGURE 28 has been developed.

FIGURE 28. Unit cell design employed in tunable capacitors.

This unit cell topology has the following key features:

- The placement of unit capacitors (C<sub>U</sub>) on both ends of the switch transistors provides two benefits. First, it allows the cell to be connected either single-ended or differentially. For our chosen balance network topology we have both series and shunt capacitances, so this flexibility is necessary. Second, this solves the problems associated with the bottom-most transistor in the stack of FIGURE 27, and allows all internal nodes to be set with a DC bias but effectively floating at the frequencies of interest. Although this approach requires four times as much physical capacitance for the same effective switched capacitance, the capacitor models available to us at the time of this design indicate that the fundamental linearity limitation in this design is the switches, not the capacitors.

- Additional coupling capacitors (C<sub>C</sub>) are placed in parallel with each of the switches. This explicit coupling adds to the intrinsic coupling, and causes the voltage swing in the off-state to be more evenly distributed across all four switches. In the on-state, the capacitors are shorted and there is little effect. For the MSB elements in the capacitor, the intrinsic coupling capacitance is relatively large and the addition of this additional C<sub>C</sub> has only a minor benefit. However, for the LSB elements in the capacitor bank, where the parasitics are larger relative to the intrinsic coupling, these coupling capacitors make an important difference in improving the efficiency and robustness of the switch design. The presence of all this extra capacitance comes at some cost in terms of C<sub>ON</sub>/C<sub>OFF</sub> ratio. However, using only the minimum capacitor size allowed by the process (33fF) significant benefit can

DUPLO WP2 D2.2 36 / 76

be achieved with only about 15% reduction in  $C_{ON}/C_{OFF}$ . Furthermore, in this design,  $C_{ON}-C_{OFF}$  matters and we can compensate for a lower  $C_{ON}/C_{OFF}$  in other ways without any penalty. Finally,  $C_C$  can be placed directly over the switch transistors in layout. This means that the vast majority of  $C_C$ 's parasitics will couple into the gate, drain, and source nodes of the underlying transistor structure, which is what we seek to increase the coupling of anyway. Effectively, this leads to zero unwanted parasitics.

• All four terminals of the switch transistors are biased with high-impedance DC biases. For RF applications, it is much better to provide a fixed DC level (while still allowing the body to be seen as a floating node at the RF frequencies of interest). It was reported in [18] that a body-contacted FET in IBM SOI technology can have as much as 20dB better harmonic distortion performance compared to a floating-body counterpart. For this reason, it is clearly better to use body-contacted devices for our application which requires maximum linearity. Although the body contacted FET requires a larger layout footprint and has more parasitics, this is more an issue for digital gates than the moderate sized switches that we're using. In our case, the area and parasitic penalties are very minor.

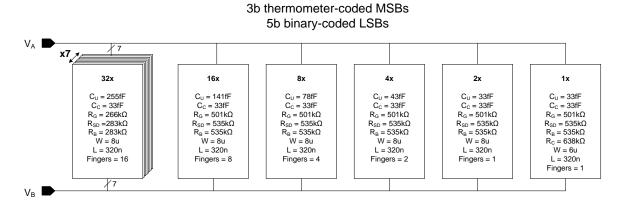

The 8b capacitor bank topology of FIGURE 29 was used for all four of the tunable capacitances implemented in the balance network.

8b Capacitor DAC

FIGURE 29. Capacitor bank overview, with design values for each sub-cell.

All sub-cells in the capacitor bank are the circuit of FIGURE 28, except for the LSB cell which uses the circuit of FIGURE 30. This special cell for the LSB stacks minimum-sized capacitors in order to create a unit capacitance that is half of the minimum capacitance allowed by the technology's design rules. Based on top-level simulations, we determined that this LSB capacitance step provides sufficient precision for the isolation requirements that the balance network must meet.

DUPLO WP2 D2.2 37 / 76

FIGURE 30. Switched capacitor unit cell used only for the LSB in the bank of FIGURE 29.

The values of all the components in the circuits of FIGURE 28 and FIGURE 30 are provided in FIGURE 29. The banks elements are scaled to a radix of 1.8x, ensuring that there will be no missing range in the capacitor bank transfer function due to random mismatch. Furthermore, the 3 most significant bits are implemented as unary-weighted capacitor elements, and the 5 least significant bits are implemented as binary-weighted elements. For this test chip, we kept the digital control of the MSBs as direct thermometer code.

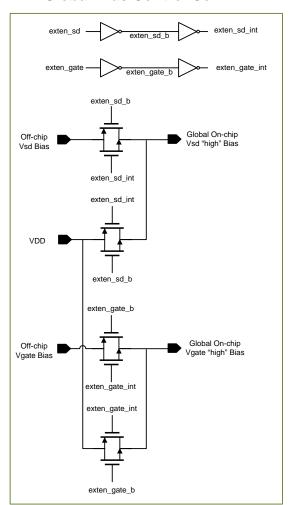

In the simplest case, the bias  $V_G$ ,  $V_B$ , and  $V_{SD}$  should be set as follows depending on the state of the capacitor cell:

|           | V <sub>G</sub> | V <sub>SD</sub> | V <sub>B</sub> |

|-----------|----------------|-----------------|----------------|

| On-state  | 2.5V           | 0V              | 0V             |

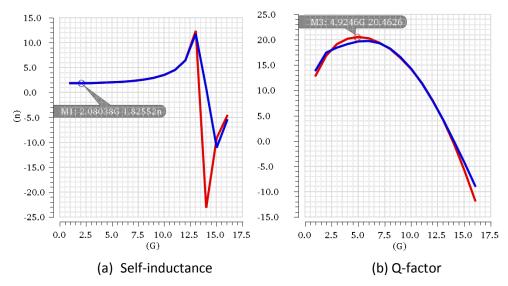

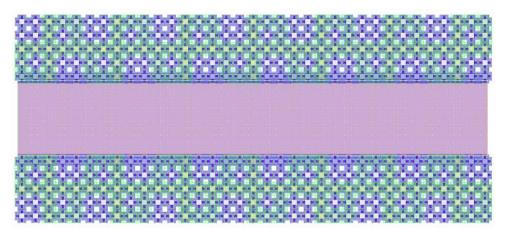

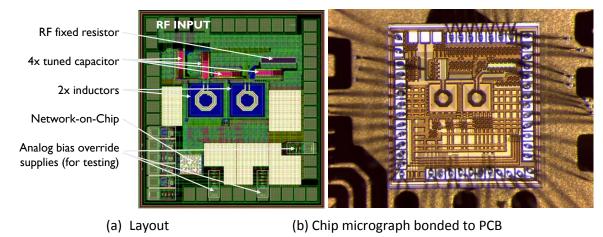

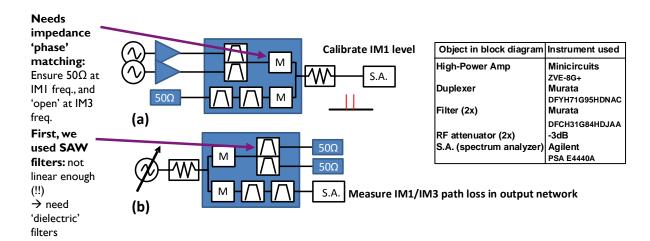

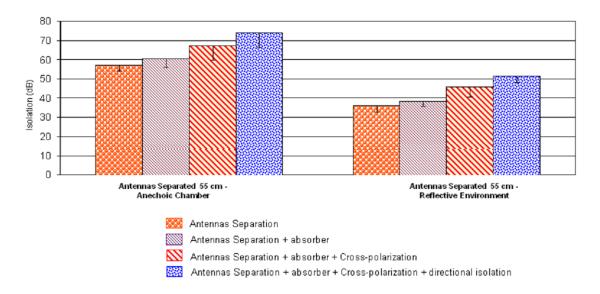

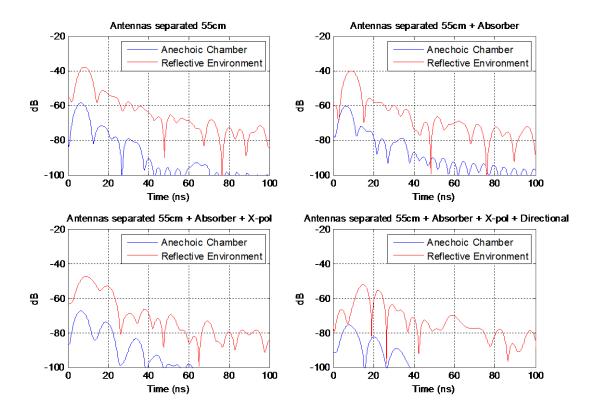

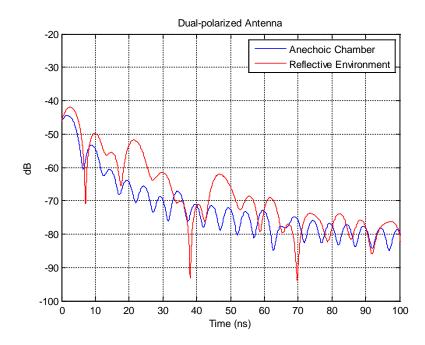

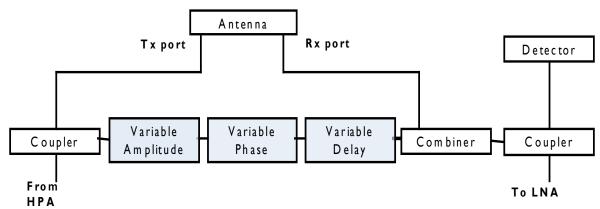

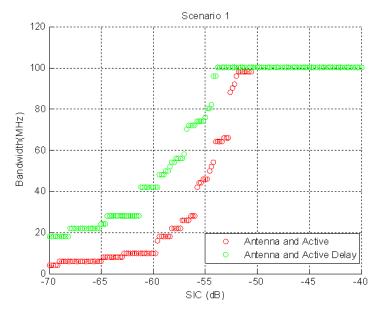

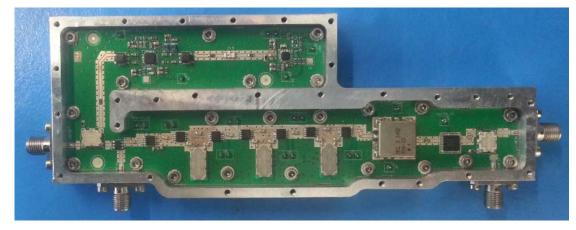

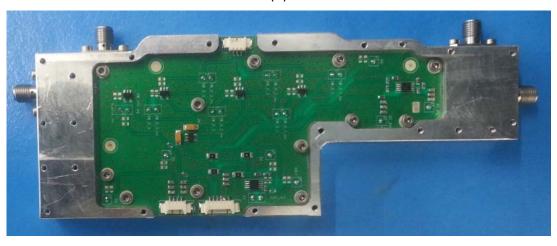

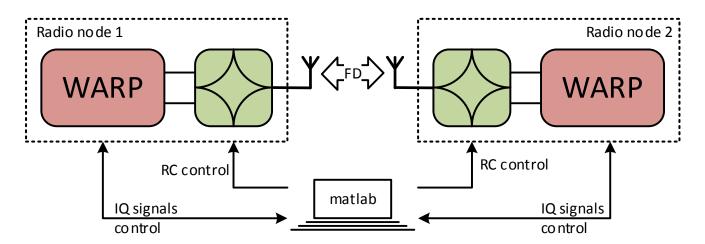

| Off-state | 0V             | 2.5V            | 0V             |